## NANO LETTERS 2007 Vol. 7, No. 10

3214-3218

## InAs/InP Radial Nanowire Heterostructures as High Electron Mobility Devices

Xiaocheng Jiang,<sup>†,§</sup> Qihua Xiong,<sup>†,§</sup> Sungwoo Nam,<sup>‡</sup> Fang Qian,<sup>†</sup> Yat Li,<sup>†</sup> and Charles M. Lieber\*,<sup>†,‡</sup>

Department of Chemistry and Chemical Biology, Harvard University, Cambridge, Massachusetts 02138, and Division of Engineering and Applied Sciences, Harvard University, Cambridge, Massachusetts 02138

Received August 13, 2007; Revised Manuscript Received August 30, 2007

## **ABSTRACT**

Radial core/shell nanowires (NWs) represent an important class of one-dimensional (1D) systems with substantial potential for exploring fundamental materials electronic and photonic properties. Here, we report the rational design and synthesis of InAs/InP core/shell NW heterostructures with quantum-confined, high-mobility electron carriers. Transmission electron microscopy studies revealed single-crystal InAs cores with epitaxial InP shells 2–3 nm in thickness, and energy-dispersive X-ray spectroscopy analysis further confirmed the composition of the designed heterostructure. Room-temperature electrical measurements on InAs/InP NW field-effect transistors (NWFETs) showed significant improvement in the on-current and transconductance compared to InAs NWFETs fabricated in parallel, with a room-temperature electron mobility, 11 500 cm²/Vs, substantially higher than other synthesized 1D nanostructures. In addition, NWFET devices configured with integral high dielectric constant gate oxide and top-gate structure yielded scaled on-currents up to 3.2 mA/µm, which are larger than values reported for other n-channel FETs. The design and realization of high electron mobility InAs/InP NWs extends our toolbox of nanoscale building blocks and opens up opportunities for fundamental and applied studies of quantum coherent transport and high-speed, low-power nanoelectronic circuits.

Central to the "bottom-up" vision for nanoscale science and technology is the design and rational synthesis of building blocks with well-defined physical properties. Semiconductor NWs represent a broad class of one-dimensional (1D) building blocks in which significant progress is being made in atomic to nanometer scale control of materials morphology, size, and composition, 1-4 including the growth of axial, 2 radial,3 and branched4 NW heterostructures. In the case of radial NW heterostructures, 3,5a-c the controlled growth of one or more shells can passivate existing surface states, enable new interface properties, and introduce unique electronic and photonic function. For example, the energy band line-up at the Ge and Si interface of Ge/Si core/shell NWs5 leads to the accumulation of high-mobility hole carriers, which have enabled fundamental studies of quantum transport 5a,b and the realization of the highest performance p-channel NWFETs to date.5c

There has also been considerable effort placed on developing high electron mobility NWs with InAs, which has a small electron effective mass and correspondingly high bulk electron mobility,6 the focus of a number of groups.7 Reported electron mobilities for InAs NWs have been substantially lower than bulk values<sup>7</sup> and thus suggest that scattering processes in the NWs, including ionized impurity and surface scattering, 7d reduce mobility. Hence, structures that passivate and/or protect the surface of InAs NWs might lead to enhanced transport properties. To this end, we report studies of InAs/InP core/shell NWs in which the InAs surfaces have been passivated with a nanometer-thick epitaxial InP conformal shell. Our design aims at creating a cylindrical quantum well populated with high-mobility electrons via a radial core/shell NW heterostructure motif. We chose InP as a shell material because the conduction band offset of ~0.52 eV provides a good confinement potential for electrons (inset, Figure 1a) and because the type-I quantum well structure also confines holes that may be generated thermally or as a result of impact ionization in the channel.<sup>8</sup> From a structural perspective, the lattice mismatch between InAs and InP is relatively large,  $\sim 3.1\%$ , and places constraints on achieving defect-free NW structures necessary for realizing high carrier mobility. Theoretical<sup>9</sup> and experimental studies 10 of planar structures suggest a critical thickness of approximately 2-3 nm, and thus we expect that

<sup>\*</sup> Corresponding author. E-mail: cml@cmliris.harvard.edu.

<sup>†</sup> Department of Chemistry and Chemical Biology.

<sup>&</sup>lt;sup>‡</sup> Division of Engineering and Applied Sciences.

<sup>§</sup> These authors contributed equally to this work.

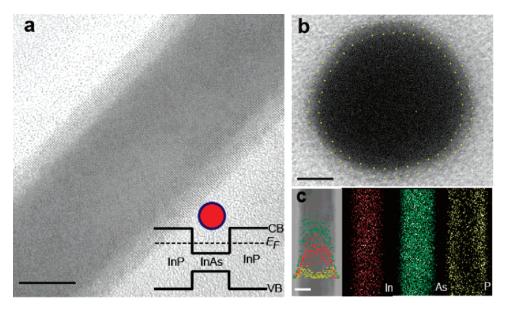

**Figure 1.** (a) HRTEM of a representative InAs/InP NW. Scale bar is 10 nm. Inset, cross-sectional schematic of an InAs/InP NW (red, InAs; blue, InP) and the corresponding band diagram. (b) Bright-field TEM image of an InAs/InP NW cross section. Dotted lines highlight the interfaces between layers. Scale bar is 5 nm. (c) Bright-field STEM image with cross-sectional EDX elemental line-scanning data (left) and the corresponding EDX elemental mapping of an InAs/InP NW. Scale bar is 10 nm.

InAs/InP core/shell NWs should remain structurally coherent when the shell thickness is near this value.

The InAs/InP core/shell NWs were prepared by a twostep synthetic methodology involving (i) Au nanoparticle catalyzed axial growth of the InAs NW core followed by (ii) radial growth of the InP shell. Clean, epitaxial growth of the InP shell was achieved using in situ source exchange and independent control of source and growth temperatures. 11 Representative high-resolution transmission electron microscopy (HRTEM) images of InAs/InP core/shell NWs (Figure 1a) show clearly contrast between InAs core and InP shell materials. The lattice-resolved images exhibit single-crystalline wurtzite structure with the growth along [001] direction. The InAs core in Figure 1a has a diameter of  $\sim$ 20 nm, while the InP shell has a thickness of  $\sim$ 2 nm. The interface between the core and shell is epitaxial and without visible dislocations, where a defect-free interface is important for achieving high electron mobility. Cross-sectional TEM images of InAs/InP NWs (Figure 1b)<sup>12</sup> further demonstrate that the InP shell is uniform around the entire InAs NW core. In addition, brightfield scanning transmission electron microscopy (STEM) images together with energy-dispersive X-ray (EDX) mapping (Figure 1c) confirms that the core/shell contrast observed in Figures 1a,b arises from the well-defined spatial distribution of As and P elements in the core and shell, respectively, of the NW structures.

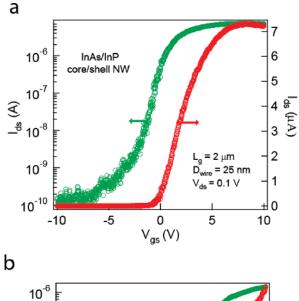

The electrical transport properties of these new InAs/InP core/shell NWs were studied initially in a NWFET configuration with back-gate electrode. <sup>13</sup> Room-temperature current ( $I_{ds}$ ) versus gate voltage ( $V_{gs}$ ) data recorded on a representative InAs/InP NW device with a total diameter of 25 nm and channel length ( $L_g$ ) of 2  $\mu$ m (Figure 2a) features an oncurrent of  $\sim$ 7  $\mu$ A and a peak transconductance ( $g_m$ ) of  $\sim$ 2.2  $\mu$ S, at a drain-source voltage of 0.1 V. For comparison,  $I_{ds}$ – $V_{gs}$  data were also recorded on InAs NW devices

fabricated in parallel using NWs having the same diameter and channel length as the core/shell structures (Figure 2b). The homogeneous InAs NWFETs exhibit a relatively large positive threshold voltage of  $\sim$ 5 V, which indicates that there is a low level of ionized dopants in our core nanowires. We note that other reported InAs NWFETs7 have shown a negative threshold voltage, which suggests substantial doping in the homogeneous NWs. Importantly, comparison of our InAs and InAs/InP devices demonstrates a shift in the threshold voltage toward  $V_{\rm gs} = 0$  and a substantial increase in on-current for the InAs/InP core/shell versus InAs NW structures. Significantly, the comparison of the  $g_{\rm m}$  values show an approximately 5-fold increase for InAs/InP (2.2  $\mu$ S) versus InAs (0.45  $\mu$ S), which corresponds to a substantially enhanced electron mobility. All these transport features are consistent with the formation of a quantum confined electron gas in the InAs/InP core/shell radial NW heterostructures.

In addition to rational band structure design, we believe that the high-quality InAs NW cores synthesized in these studies are also important to achieving high-performance devices. Logarithmic scale plots of  $I_{\rm ds}$ – $V_{\rm gs}$  curves for both InAs and InAs/InP NW devices (Figure 2a,b, green lines) exhibit off-current <0.2 nA and subthreshold slopes (S) < 1 V/decade. Most reported InAs NW devices have shown much larger off-currents (>1  $\mu$ A) and poor subthreshold behavior (S > 3 V/decade), possibly due to the incorporation of dopants and/or vacancies during growth. <sup>7a-c</sup> Our ability to optimize InAs NW cores independently of the InP shell growth was critical to realizing this behavior in our studies, and we believe further efforts in this direction (i.e., improving the InAs NW purity) could yield additional improvements in the device properties.

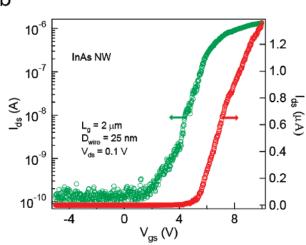

Temperature-dependent electrical transport measurements were carried out to further characterize the InAs/InP NWs. Conductance (G) vs  $V_{\rm gs}$  data (Figure 3a) show that the on-

**Figure 2.** (a)  $I_{ds}-V_{gs}$  data for a 25 nm diameter InAs/InP NW back-gated FET with  $L_{\rm g}=2~\mu{\rm m}$  at  $V_{\rm ds}=0.1~{\rm V}$ , plotted on linear (red) and logarithmic (green) scales. (b)  $I_{\rm ds} - V_{\rm gs}$  data for a 25 nm diameter InAs NW back-gated FET fabricated in parallel with same channel length, plotted on linear (red) and logarithmic (green) scales.

state conductance, ca. 40 µS, changes little as temperature decreases. This fact implies that the number of 1D subbands participating in transport does not vary with decreasing the temperature. We also find that the threshold voltage exhibits a small shift for T > 100 K. This shift may reflect a freezeout of surface states<sup>14</sup> and would be consistent with the larger than theoretical value of S discussed above. The temperaturedependence of the field-effect electron mobility (Figure 3b), which was calculated using the charge control model, 15,16 shows that the electron mobility of the InAs/InP NW devices increases from 11 500 cm<sup>2</sup>/Vs at room temperature and then saturates at  $18\,000$  cm<sup>2</sup>/Vs for T < 100 K. It is worth mentioning that contact resistance was not taken into account in our mobility values and thus that higher mobility values could be achieved by subtracting this series resistance term and/or optimization of contact transparency.

The temperature-dependent mobility results obtained for our InAs/InP core/shell NWs are distinct from those commonly observed in uniformly doped III-V materials, 17 which show carrier freeze-out and dramatically lower mobility for T < 100 K but similar to two-dimensional electron gas

**Figure 3.** (a)  $G-V_{\rm gs}$  data measured at temperatures from 300 to 10 K for a 25 nm diameter InAs/InP back-gated NWFET with  $L_{g}$ = 4  $\mu$ m. (b) Calculated electron mobility of the InAs/InP NW at different temperatures. 16 For comparison, the highest room-temperature electron mobility values reported in other 1D nanostructures are also included.

InAs NW by Bryllert et al.

InAs NW by Dayeh et al.

5 6 7

T (K)

100

◩

n-SWNT by Javey et al.

5

0

10

(2DEG) systems studied extensively using planar heterostructures.<sup>17</sup> These comparisons provide evidence for 1DEG formation in the InAs/InP NW heterostructures. We also note that core/shell NW electron mobility shows a weaker temperature dependence before saturation than classical 2DEGs.<sup>16</sup> This fact indicates that (i) ionized impurity and interface scattering, which dominate in the low-temperature regime, may limit electron mobility in our devices and (ii) phonon scattering has been substantially suppressed in our 1D structures. 18 Future work focused on improving the purity of the InAs NW core and epitaxial shell growth should help to address better the origins of these differences with 2DEG

Our data can also be compared to recent electron mobility values reported in other n-channel NW and carbon nanotube devices (Figure 3b). Bryllert et al. reported an electron mobility of  $\sim 3000 \text{ cm}^2/\text{Vs}$  in vertical InAs NW transistors with novel cylindrical gate structure, 7a while Dayeh et al. reported a similar value of  $\sim$ 2740 cm<sup>2</sup>/Vs in back-gated InAs

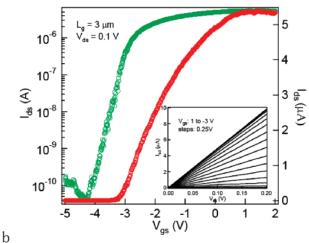

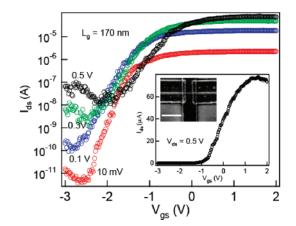

**Figure 4.** (a)  $I_{\rm ds}-V_{\rm gs}$  data for a 25 nm diameter InAs/InP nanowire top-gate FET with  $L_{\rm g}=3~\mu{\rm m}$  at  $V_{\rm ds}=0.1~{\rm V}$ , plotted on linear (red, right) and logarithmic (green, left) scales. Inset:  $I_{\rm ds}-V_{\rm ds}$  data recorded at  $V_{\rm gs}$  values from +1.0 to  $-3.0~{\rm V}$  in steps of 0.25 V. (b)  $I_{\rm ds}-V_{\rm gs}$  data for a 25 nm diameter InAs/InP NW top-gated FET with  $L_{\rm g}=170~{\rm nm}$ , in which red, blue, green, and black data points correspond to  $V_{\rm ds}$  values of 0.01, 0.1, 0.3, and 0.5 V, respectively. Inset: linear scale plot of  $I_{\rm ds}$  versus  $V_{\rm gs}$  measured at  $V_{\rm ds}=0.5~{\rm V}$  with top-view SEM image of the device. Scale bar is 500 nm.

NWFETs.<sup>7c,19</sup> The highest electron mobility in carbon nanotubes (CNTs) is ~1000 cm²/Vs.<sup>20</sup> The 11 500 cm²/Vs room-temperature electron mobility in our InAs/InP NW heterostructures, which represents a lower-bound value without contact resistance correction, is significantly higher

than reported electron mobility data for these other 1D nanostructures and thus further substantiates the promise of the our radial core/shell approach for creating unique nanoscale building blocks.

NWFET devices with a top metal gated structure incorporating high- $\kappa$  dielectric were fabricated to explore the potential of our InAs/InP NWs as high-performance FETs. Typical  $I_{\rm ds}-V_{\rm ds}$  curves (Figure 4a, inset) are linear at all measured gate voltages, indicating that the contacts are ohmic in our devices. These data also show that  $I_{\rm ds}$  increases as  $V_{\rm gs}$  increases from -3 to 1 V and thus that the device functions as an n-channel depletion-mode FET. The  $I_{\rm ds}-V_{\rm gs}$  transfer curve recorded at  $V_{\rm ds}=0.1$  V (Figure 4a) exhibits a peak transconductance  $g_{\rm m}$  of  $\sim 3.0~\mu{\rm S}$  and a subthreshold slope S of  $\sim 180~{\rm mV/decade}$  for this  $L_{\rm g}=3~\mu{\rm m}$  device. Both values are substantially better than achieved with comparable backgate devices (Figure 2).

We have also fabricated shorter channel length InAs/InP NWFET devices to investigate scaling of critical device properties. Representative  $I_{\rm ds}$  –  $V_{\rm gs}$  curves recorded at different  $V_{\rm ds}$  obtained from an  $L_{\rm g}=170$  nm device (Figure 4b) show an on-off ratio (>10<sup>5</sup>) and  $S \sim 80$  mV/decade for  $V_{\rm ds} = 10$ mV; these values decreased/increased to 10<sup>3</sup>/260 mV/decade as  $V_{\rm ds}$  increased to 0.5 V. This trend indicates a nonnegligible short-channel effect in our device.<sup>22</sup> In addition, the maximum  $I_{\rm on} = 79 \ \mu \text{A}$  and  $g_{\rm m} = 63 \ \mu \text{S}$  (inset, Figure 4b) yield scaled<sup>5c</sup> values of  $I_{\rm on}$ , 3.2 mA/ $\mu$ m, and  $g_{\rm m}$ , 2.5 mS/  $\mu$ m, that are substantially higher than other NW and nanotube FETs<sup>5c,20b,23</sup> or n-channel MOSFETs.<sup>24</sup> A comparison of key parameters obtained for our InAs/InP core/shell and other high-performance FETs are summarized in Table 1. Notably, the scaled  $I_{\rm on}$  value (38 mA/ $\mu$ m) exceeds substantially other systems and demonstrates the potential of InAs/InP NWFETs, assuming that short-channel effects can be overcome via improved device structure design.<sup>24,25</sup>

In summary, we have designed and synthesized single-crystal InAs/InP core/shell NW heterostructures with quantum-confined, high-mobility electron carriers. Transmission electron microscopy studies revealed single-crystal InAs cores with epitaxial InP shells 2–3 nm in thickness, and energy-dispersive X-ray spectroscopy analysis further confirmed the composition of the designed heterostructure. Systematic transport studies confirmed the core/shell NW band-structure design, demonstrated significant improvement of the on-current and transconductance compared to InAs NWFETs,

Table 1. Main FET Characteristics of Our InAs/InP Device and Those Reported in Other 1D Nanostructures and Planar CMOS

|                                                | InAs/InP<br>NW | n-carbon nanotube<br>(moderate doping) | n-carbon nanotube<br>(high doping) | GaN/AlN/AlGaN<br>NW | Ge/Si<br>p-NW | planar<br>CMOS |

|------------------------------------------------|----------------|----------------------------------------|------------------------------------|---------------------|---------------|----------------|

| gate length (nm)                               | 170            | 80                                     | 80                                 | 1000                | 190           | 35             |

| $V_{ m ds}\left( m V ight)$                    | 0.5            | 0.5                                    | 0.5                                | 1.5                 | 1.0           | 1.2            |

| $I_{\rm on}  ({\rm mA/}\mu{\rm m})$            | 3.2            | 0.3                                    | 2.0                                | 0.5                 | 2.1           | 1.75           |

| converted $I_{\rm on}~({\rm mA}/\mu{\rm m})^a$ | 38             | 1.7                                    | 11                                 | 11                  | 14            | 1.75           |

| on/off ratio                                   | $10^{3}$       | $10^4$                                 | $10^2$                             | $10^{7}$            | $10^{3}$      | $10^{4}$       |

| $subthreshold\ slope\ (mV/decade)$             | 260            | 70                                     | 300                                | 68                  | 100           | 150            |

<sup>&</sup>lt;sup>a</sup> For direct comparison, we calculated the converted  $I_{\rm on}$  value by scaling to the drive voltage (1.2 V) and dimensions ( $L_{\rm g}=35$  nm) of a state-of-the-art MOSFET (column 7), assuming (i)  $I_{\rm on}$  is proportional to  $V_{\rm sd}$ , (ii) the contact resistance is much smaller than the channel resistance, and (iii) the resistance of channel is proportional to length.

and yielded the highest electron mobility value to date,  $11\,500~{\rm cm^2/Vs}$  at room temperature, for 1D nanoscale building blocks. In addition, NWFET devices configured with integral high dielectric constant gate oxide and metal topgate structure yielded scaled on-currents up to  $3.2~{\rm mA/\mu m}$ , which are larger than values reported for other n-channel FETs. The design and realization of high electron mobility InAs/InP NWs extends our toolbox of nanoscale building blocks and could open up opportunities for fundamental and applied studies of quantum coherent transport and high-speed, low-power nanoelectronic circuits.

**Acknowledgment.** We thank J. Xiang, H. Yan and X. Gao for helpful discussions. C.M.L. acknowledges support of this work by Defense Advanced Research Projects Agency and Samsung Electronics Corporation.

**Note Added after ASAP Publication.** There was an error in the equation in ref 16 that appeared in the version published ASAP September 15, 2007; the corrected version was published ASAP September 17, 2007.

## References

- (1) (a) Hu, J.; Odom, T.; Lieber, C. M. Acc. Chem. Res. 1999, 32, 435.

(b) Lieber, C. M. MRS Bull. 2003, 28, 486. (c) Li, Y.; Qian, F.; Xiang, J.; Lieber, C. M. Mater. Today 2006, 9, 18.

- (2) (a) Gudiksen, M. S.; Lauhon, L. J.; Wang, J.; Smith, D. C.; Lieber, C. M. Nature 2002, 415, 617. (b) Wu, Y.; Fan, R.; Yang, P. Nano Lett. 2002, 2, 83. (c) Bjork, M. T.; Ohlsson, B. J.; Sass, T.; Persson, A. I.; Thelander, C.; Magnusson, M. H.; Deppert, K.; Wallenberg, L. R.; Samuelson, L. Appl. Phys. Lett. 2002, 80, 1058.

- (3) Lauhon, L. J.; Gudiksen, M. S.; Wang, D.; Lieber, C. M. Nature 2002, 420, 57.

- (4) (a) Dick, K. A.; Deppert, K.; Larsson, M. W.; Martensson, T.; Seifert, W.; Wallenberg, L. R.; Samuelson, L. Nat. Mater. 2004, 3, 380. (b) Wang, D.; Qian, F.; Yang, C.; Zhong, Z. H.; Lieber, C. M. Nano Lett. 2004, 4, 871.

- (5) (a) Lu, W.; Xiang, J.; Timko, B. P.; Wu, Y.; Lieber, C. M. Proc. Natl. Acad. Sci. U.S.A. 2005, 102, 10046. (b) Xiang, J.; Vidan, A.; Tinkham, M.; Westervelt, R. M.; Lieber, C. M. Nat. Nanotechnol. 2006, 1, 208. (c) Xiang, J.; Lu, W.; Hu, Y. J.; Wu, Y.; Yan, H.; Lieber, C. M. Nature 2006, 441, 489.

- (6) Sze, S. M. Physics of Semiconductor Devices, 2nd ed.; John Wiley & Sons: New York, 1981.

- (7) (a) Bryllert, T.; Wernersson, L. E.; Froberg, L. E.; Samuelson, L. IEEE Electron Device Lett. 2006, 27, 323. (b) Lind, E.; Persson, A. I.; Samuelson, L.; Wernersson, L. E. Nano Lett. 2006, 6, 1842. (c) Dayeh, S. A.; Aplin, D. P. R.; Zhou, X. T.; Yu, P. K. L.; Yu, E. T.; Wang, D. L. Small 2007, 3, 326. (d) Thelander, C.; Bjork, M. T.; Larsson, M. W.; Hansen, A. E.; Wallenberg, L. R.; Samuelson, L. Solid State Commun. 2004, 131, 573.

- (8) Davies, J. H. The Physics of Low-Dimensional Semiconductors: An Introduction; Cambridge University Press: Cambridge, UK, 1997.

- (9) Matthews, J. W.; Blakesleee, A. E. J. Cryst. Growth 1974, 27, 118.

- (10) (a) Kobayashi, Y.; Kobayashi, N. Jpn. J. Appl. Phys. 1992, 31, 3988.

(b) Hopkinson, M.; David, J. P. R.; Claxton, P. A.; Kightley, P. Appl. Phys. Lett. 1992, 60, 841.

- (11) Thermal evaporation and vapor transport method were used for the synthesis of InAs/InP NWs. The synthesis set-up includes a twozone tube furnace (with zone I at upstream and zone II at downstream) and an in situ source exchange unit. In a typical growth, a few grams

- of InAs and InP powders (Alfa Aesar) were loaded into two individual quartz transfer tubes located at the upstream end of the reactor, while a Si/SiO2 substrate with well dispersed 10 nm gold nanoclusters (Ted Pella) was placed into zone II of the tube furnace. The reactor was then evacuated to 15 mTorr, heated up to the set temperature, and maintained at a certain pressure with H2 flow. For the InAs core synthesis, after zone I and zone II had reached set temperatures of 690 and 530 °C, respectively, the transfer tube with InAs powder was inserted into the center of zone I to initiate the growth. A total pressure of 2 torr was maintained during the growth process, with a 20 sccm flow of H2. After 40 min, the axial growth of InAs NW was terminated by pulling out the transfer tube with InAs source. Then, the furnace temperature was reset to be 710 and 500 °C for zone I and zone II, respectively, and the transfer tube with InP powder was inserted into zone I to start the InP shell deposition. The deposition time is controlled to be 2 min, corresponding to the formation of a  $\sim$ 2 nm InP shell according to TEM analysis.

- (12) Qian, F.; Gradecak, S.; Li, Y.; Wen, C.; Lieber, C. M. Nano Lett. 2005, 5, 2287.

- (13) InAs/InP and InAs NW FETs were fabricated on a degenerately doped silicon substrate with 50 nm SiO<sub>2</sub> dielectric layer. Electron beam lithography was used to define the electrical contacts, followed by HF etching (1:1000 diluted in DI water from commercial avalaible 48% HF solution, etching time  $\sim$ 3 s) and thermal evaporation of Ti/Al (10/500 Å) metals.

- (14) Liu, C. H.; Lee, M. T.; Lin, C. Y.; Chen, J.; Loh, Y. T.; Liou, F. T.; Schruefer, K.; Katsetos, A. A.; Yang, Z. J.; Rovedo, N.; Hook, T. B.; Wann, C.; Chen, T. C. *Jpn. J. Appl. Phys.* **2002**, *41*, 2423.

- (15) Martel, R.; Schmidt, T.; Shea, H. R.; Hertel, T.; Avouris, Ph. Appl. Phys. Lett. 1998, 73, 2447.

- (16) According to charge control model,  $dI/dV_g = g_m = \mu (C_g/L_g^2)V_{ds}$ , where  $\mu$  is the mobility and  $C_g$  is the gate capacitance. For current case,  $L_g = 4 \mu m$ ,  $V_{ds} = 0.1 \text{ V}$ , and the  $C_g$  value was estimated using the Quickfield program. For a 25 nm diameter InAs/InP nanowire (21 nm diameter InAs core and 2 nm InP shell) on a degeneratively doped Si substrate with 50nm SiO<sub>2</sub> dielectric layer in a global backgate configuration, the calculation yields a value of  $\sim$ 52 aF/ $\mu$ m.

- (17) Pfeiffer, L.; West, K. W.; Stormer, H. L.; Baldwin, K. W. Appl. Phys. Lett. 1989, 55, 1888.

- (18) Sakaki, H. Jpn. J. Appl. Phys. 1980, 19, L735.

- (19) Reference 7c also reported electron mobility value of ~6580 cm²/ Vs in top-gate devices. This value was calculated using a different method from other results; we have compared value calculated in a similar manner for consistency.

- (20) (a) Javey, A.; Kim, H.; Brink, M.; Wang, Q.; Ural, A.; Guo, J.; McIntyre, P.; McEuen, P.; Lundstrom, M.; Dai, H. J. *Nat. Mater.* 2002, *I*, 241. (b) Javey, A.; Tu, R.; Farmer, D. B.; Guo, J.; Gordon, R. G.; Dai, H. J. *Nano Lett.* 2005, *5*, 345.

- (21) The high-κ dielectric was deposited via atomic layer deposition (ALD). Tetrakis(dimethylamino) hafnium was used as the precursor, and 50 cycles HfO<sub>2</sub> deposition were carried out at 110 °C, with each cycle consisting of a 1 s water vapor pulse, a 5 s nitrogen purge, a 3 s precursor, and a 5 s nitrogen purge. Electron beam lithography was used to define top-gate electrodes, followed by thermal evaporation of Ti/Au (5 nm/50 nm) as the gate metal. The top gate overlaps with the source/drain electrodes to ensure full coverage of the channel.

- (22) Brennan, K. F.; Brown, A. S. Theory of Modern Electronic Semiconductor Devices; John Wiley & Sons: New York, 2002.

- (23) Li, Y.; Xiang, J.; Qian, F.; Gradecak, S.; Wu, Y.; Yan, H.; Blom, D. A.; Lieber, C. M. Nano Lett. 2006, 6, 1468.

- (24) Ranade, P.; Ghani, T.; Kuhn, K.; Mistry, K.; Pae, S.; Shifren, L.; Stettler, M.; Tone, K.; Tyagi, S.; Bohr, M. *IEDM Tech. Dig.* 2005, 217.

- (25) Kavalieros, J.; Doyle, B.; Datta, S.; Dewey, G.; Doczy, M.; Jin, B.; Lionberger, D.; Metz, M.; Rachmady, W.; Radosavljevic, M.; Shah, U.; Zelick, N.; Chau, R. VLSI Tech. Dig. 2006, 50.

NL072024A